1. 서 론

1.1 연구배경 및 목적

2. 계통에 의한 dc-link 단의 AC 리플 분석

3. 노치 필터 설계

3.1 아날로그 노치 필터 설계

3.2 디지털 노치 필터 설계

4. 시뮬레이션

5. 결 론

1. 서 론

1.1 연구배경 및 목적

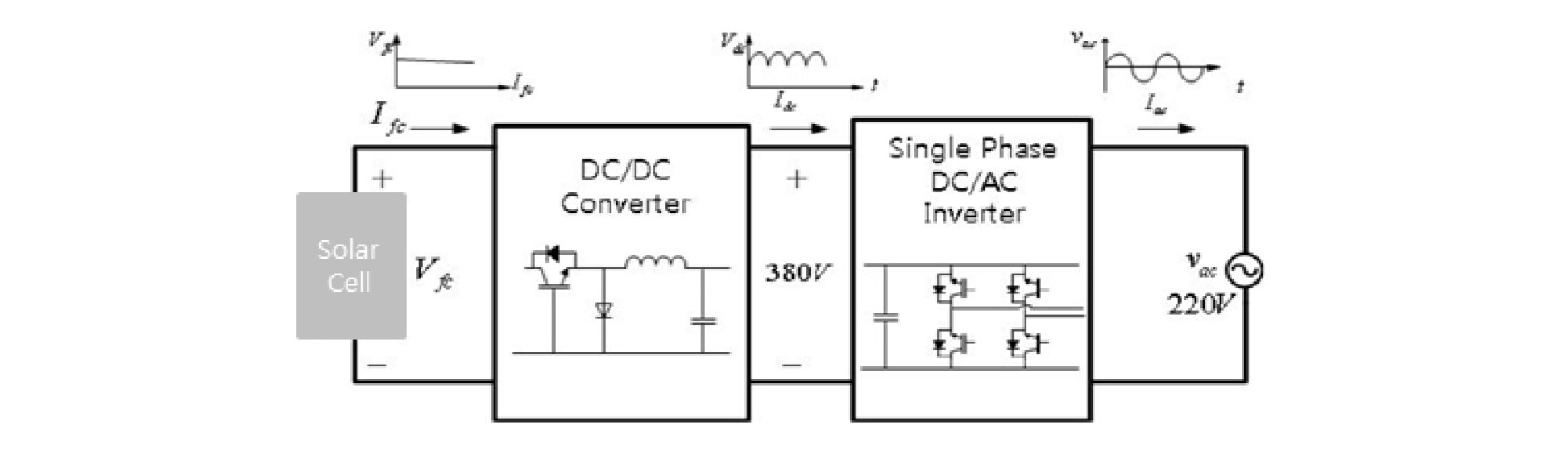

지구 환경문제에 의한 기후변화와 화석 연료의 고갈 및 원자력 발전소의 위험성 대두로 인해 풍력, 태양광 발전 등과 같은 신재생 에너지가 대체재로 떠오르고 있다. 태양광 발전 중에서 Fig. 1과 같이 단상 태양광 인버터를 계통과 연결해 계통 연계형 인버터 PVPCS (Photovoltaic Power Conditioning System)로 운전시키는 경우 계통에 의해 dc-link 단에 계통의 주파수의 2배에 해당하는 120 Hz의 AC 리플이 발생한다. 이러한 120 Hz AC 리플은 커패시터의 수명을 단축하게 하며 PVPCS의 출력전류의 THD(Total Harmonic Distortion)를 증가시킨다. 이러한 원인은 PVPCS의 효율을 저하시키므로 노치 필터를 이용하여 계통에 의한 120 Hz의 리플 성분을 제거한다. 디지털 노치 필터를 설계하는 경우 샘플링 주파수, 대역폭, 감쇠폭에 가장 큰 영향을 받는다. 그중 샘플링 주파수는 스위칭 주파수의 역수로 계산한다. 스위칭 주파수 에 따라 PVPCS의 LC 필터 크기가 결정되며, 전력용 반도체 스위치의 스위칭 손실이 결정된다. 높은 스위칭 주파수를 사용할 경우 인버터 출력전압의 가장 큰 고조파 차수가 증가하므로 크기가 작은 LC 필터에 의해 쉽게 필터링 되어 전압 파형의 질이 좋아진다. 하지만 스위칭 손실의 증가로 인해 출력전류의 THD가 낮아져도 전체 시스템의 효율이 감소한다. 반대로 낮은 스위칭 주파수를 사용할 경우 스위칭 손실은 감소하지만, LC 필터 크기가 커진다. 따라서 시스템의 전체 성능을 고려한 스위칭 주파수를 선정하는 것이 중요하다. 본 논문에서는 단상 PVPCS의 출력전류의 THD와 스위칭 손실에 따른 최적의 노치 필터를 설계하고, 이를 시뮬레이션을 통해 검증했다.

2. 계통에 의한 dc-link 단의 AC 리플 분석

계통의 전압과 전류를 식(1)과 같이 정의하고, dc-link 단의 전력과 인버터 출력 전력을 계산하면 식(2)로 나타낼 수 있다1,2.

| $$V_{ac}=V_m\sin\omega t,\;I_{ac}=I_m\sin\omega t$$ | (1) |

| $$P_{dc}=V_{dc}I_{dc},\;P_{ac}=V_mI_m\sin^2\omega t=\frac{V_mI_m}2(1-\cos2\omega t)$$ | (2) |

인버터에서 스위칭 손실이나 다른 손실이 발생하지 않고 이상적으로 동작한다고 가정하면 dc-link 단 전력과 인버터 출력 전력이 같다. 일 때 dc-link 단 전류 는 식(3)과 같이 계산할 수 있다.

| $$I_{dc}=\frac{V_mI_m}{2V_{dc}}(1-\cos2\omega t)=\frac{V_mI_m}{2V_{dc}}-\frac{V_mI_m}{2V_{dc}}(1-\cos2\omega t)=I_{DC}+I_{dc(ac)}$$ | (3) |

결국, dc-link 단에 발생하는 전압 리플은 식(4)와 같이 에 의해 커패시터 에 걸리는 전압의 크기임을 확인할 수 있다.

| $$V_{dc}=\frac1{C_{dc}}\int_{}^{}-I_{dc(ac)}dt=\frac{V_mI_m}{4\omega C_{dc}V_{dc}}\sin2\omega t$$ | (4) |

3. 노치 필터 설계

3.1 아날로그 노치 필터 설계

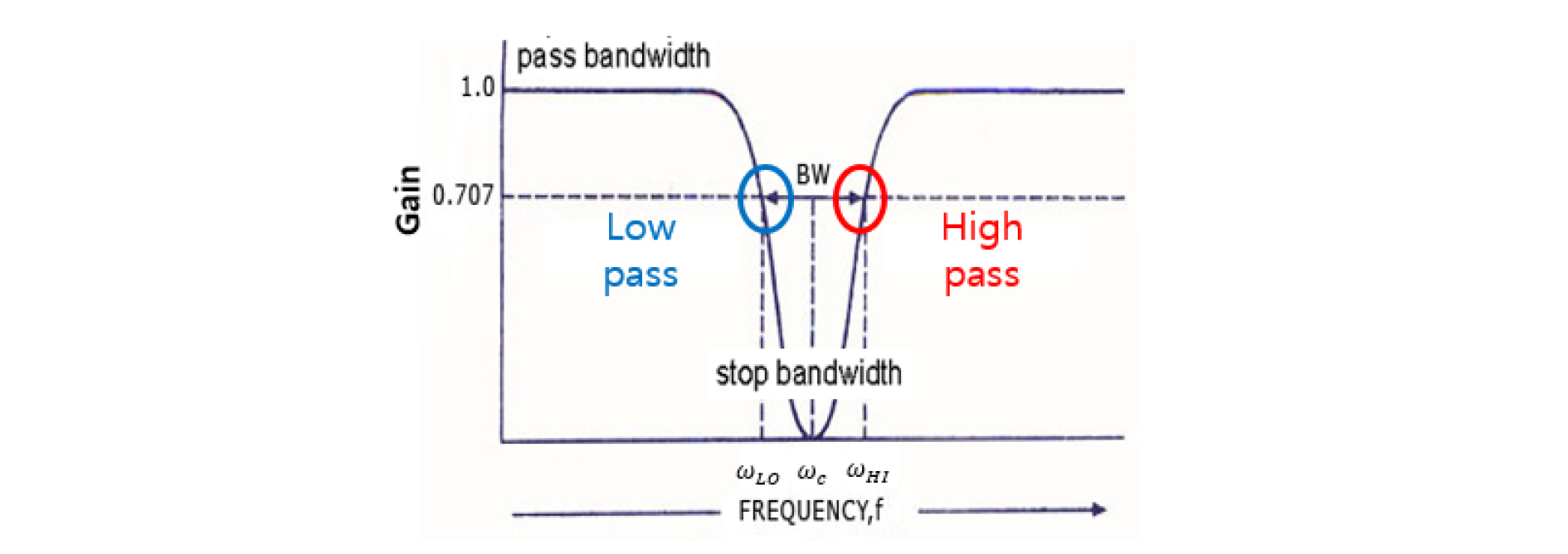

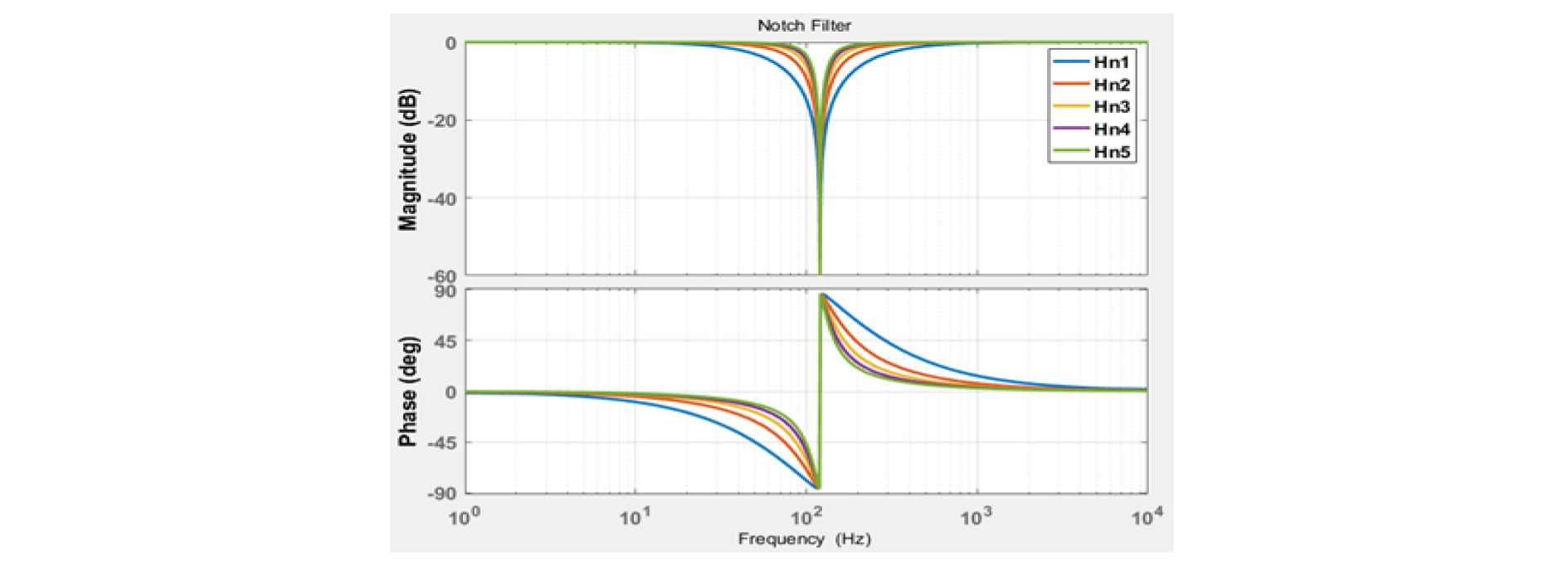

노치 필터는 Fig. 2의 보데 선도와 같이 특정 주파수에서 급격한 감쇠 특성을 가지며, 원하지 않는 특정 주파수를 제거하는 데 그 목적이 있다. 노치 필터는 저역 통과 필터와 고역 통과 필터의 조합으로 이뤄지며 식(5)와 같이 2-zero, 2-pole을 갖는 2차 전달 함수로 표현할 수 있다3.

| $$H(s)=\frac{s^2+2\xi_z\omega_0s+\omega_o^2}{s^2+2\xi_p\omega_0s+\omega_o^2}$$ | (5) |

식(5)에서 는 공진(차단) 주파수이며, 는 노치 필터의 깊이, 는 노치 필터의 폭에 관한 상수이다. 의 크기가 작을수록 필터의 깊이가 깊어지며 감쇠율이 높아진다. 또한 는 대역폭에 관한 상수이므로 크기가 커질수록 필터의 대역폭이 넓어진다. 식(5)를 해석과 설계의 편의를 위해 식(6)의 형태로 표현할 수 있다.

| $$H(s)=\frac{s^2+2{\displaystyle\frac dc}\omega_0s+\omega_o^2}{s^2+2{\displaystyle\frac1c}\omega_os+\omega_o^2}$$ | (6) |

식(6)의 전달 함수를 주파수 영역에서 표현하면 이며 공진 주파수 에서의 전달 함수의 크기는 이므로 는 감쇠 정도, 는 대역폭의 상수임을 확인할 수 있다.

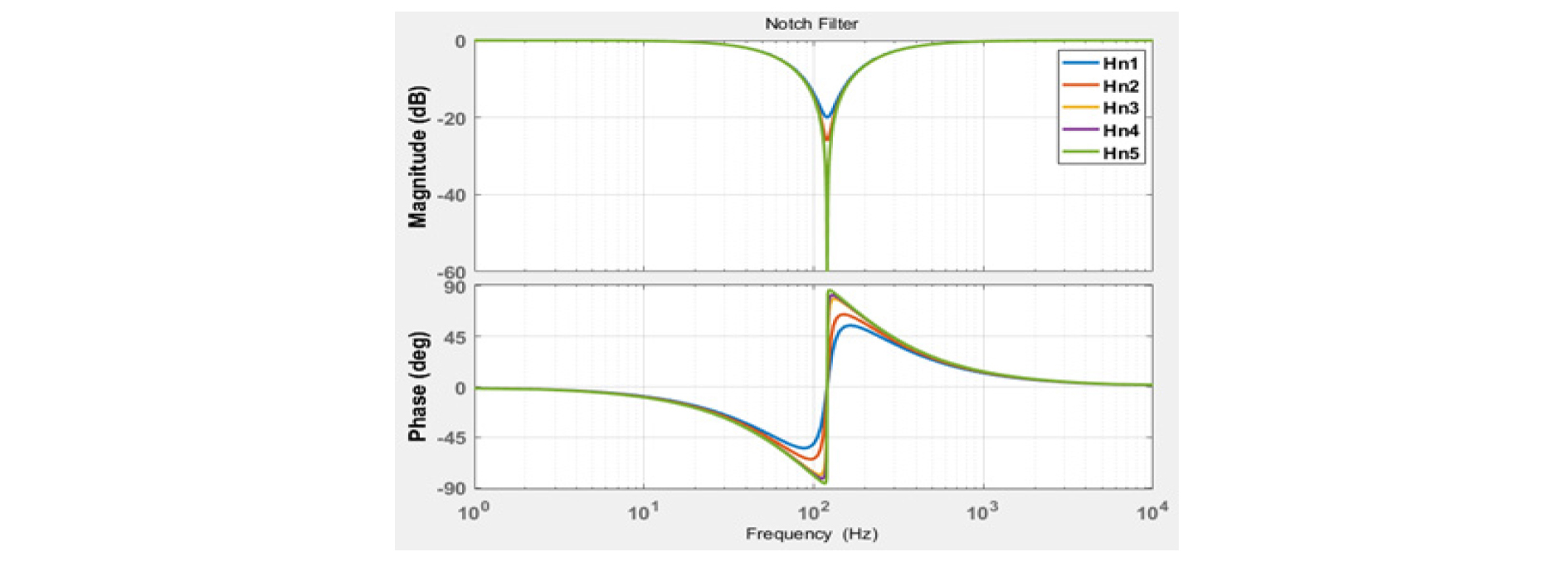

Fig. 3과 Table 1은 의 변화에 따른 노치 필터의 보데 선도와 필터의 감쇠 정도를 나타내고 있으며 가 작을수록 필터의 감쇠가 크게 이뤄짐을 확인할 수 있다. 또한 Fig. 4와 Table 2는 의 변화에 따른 노치 필터의 보데 선도와 필터의 대역폭을 나타내며 가 클수록 필터의 대역폭이 넓어짐을 확인할 수 있다.

Table 1 The depth of the notch filter according to the value of d

| fc | d | c | Depth | |

| Hn1 | 120 Hz | 0.1 | 1.0 | -20 dB |

| Hn2 | 120 Hz | 0.05 | 1.0 | -26 dB |

| Hn3 | 120 Hz | 0.01 | 1.0 | -40 dB |

| Hn4 | 120 Hz | 0.005 | 1.0 | -46 dB |

| Hn5 | 120 Hz | 0.001 | 1.0 | -60 dB |

Table 2 The bandwidth of the notch filter according to the value of c

| fc | d | c | Depth | Width | |

| Hn1 | 120 Hz | 0.001 | 1.0 | -60 dB | 340 Hz |

| Hn2 | 120 Hz | 0.001 | 2.0 | -60 dB | 148 Hz |

| Hn3 | 120 Hz | 0.001 | 3.0 | -60 dB | 94 Hz |

| Hn4 | 120 Hz | 0.001 | 4.0 | -60 dB | 68 Hz |

| Hn5 | 120 Hz | 0.001 | 5.0 | -60 dB | 52 Hz |

3.2 디지털 노치 필터 설계

아날로그 노치 필터의 s-domain의 전달 함수를 디지털 노치 필터로 구현하기 위해서는 z-domain의 전달 함수로 변환해야 한다. 본 논문에서는 Bilinear Transform을 이용해 s-domain의 전달 함수를 z-domain의 전달 함수로 변환한다. 따라서 식 (5)에 을 대입하여 식 (7)의 형태의 전달 함수로 변환한다.

| $$H(z)=\frac{T(z)}{X(z)}=\frac{b_0+b_1z^{-1}+b_2z^{-2}}{1+\alpha_1z^{-1}+\alpha_2z^{-2}}$$ | (7) |

이때 T는 Sampling Time이며 스위칭 주파수 의 역수로 계산한다.

Bilinear Transform을 이용해 s-domain의 전달함수를 z-domain의 전달 함수로 변환했을 때 식(7)의 각 계수는 식(8-1) ~ (8-5)로 표현된다.

| $$\alpha_1=\frac{{\displaystyle\frac{-8}{T^2}}+2\omega_0^2}{{\displaystyle\frac4{T^2}}+{\displaystyle\frac{4\xi_p}T}+\omega_0^2}$$ | (8-1) |

| $$\alpha_2=\frac{{\displaystyle\frac4{T^2}}-{\displaystyle\frac{4\zeta_p}T}+\omega_0^2}{{\displaystyle\frac4{T^2}}+{\displaystyle\frac{4\zeta_p}T}+\omega_0^2}$$ | (8-2) |

| $$b_0=\frac{{\displaystyle\frac4{T^2}}+{\displaystyle\frac{4\zeta_z}T}+\omega_0^2}{{\displaystyle\frac4{T^2}}+{\displaystyle\frac{4\zeta_p}T}+\omega_0^2}$$ | (8-3) |

| $$b_1=\frac{{\displaystyle\frac{-8}{T^2}}+2\omega_0^2}{{\displaystyle\frac4{T^2}}+{\displaystyle\frac{4\zeta_p}T}+\omega_0^2}$$ | (8-4) |

| $$b_2=\frac{{\displaystyle\frac4{T^2}}-{\displaystyle\frac{4\zeta_z}T}+\omega_0^2}{{\displaystyle\frac4{T^2}}+{\displaystyle\frac{4\zeta_p}T}+\omega_0^2}$$ | (8-5) |

z-domain의 전달 함수를 출력 변수 로 표현하고 디지털 연산을 위한 이산 방정식으로 나타내면 식(9)와 같다.

| $$y(t)=-\alpha_1y(t-T)-\alpha_2y(t-2T)+b_0x(t)+b_1x(t-T)+b_2x(t-2T)$$ | (9) |

4. 시뮬레이션

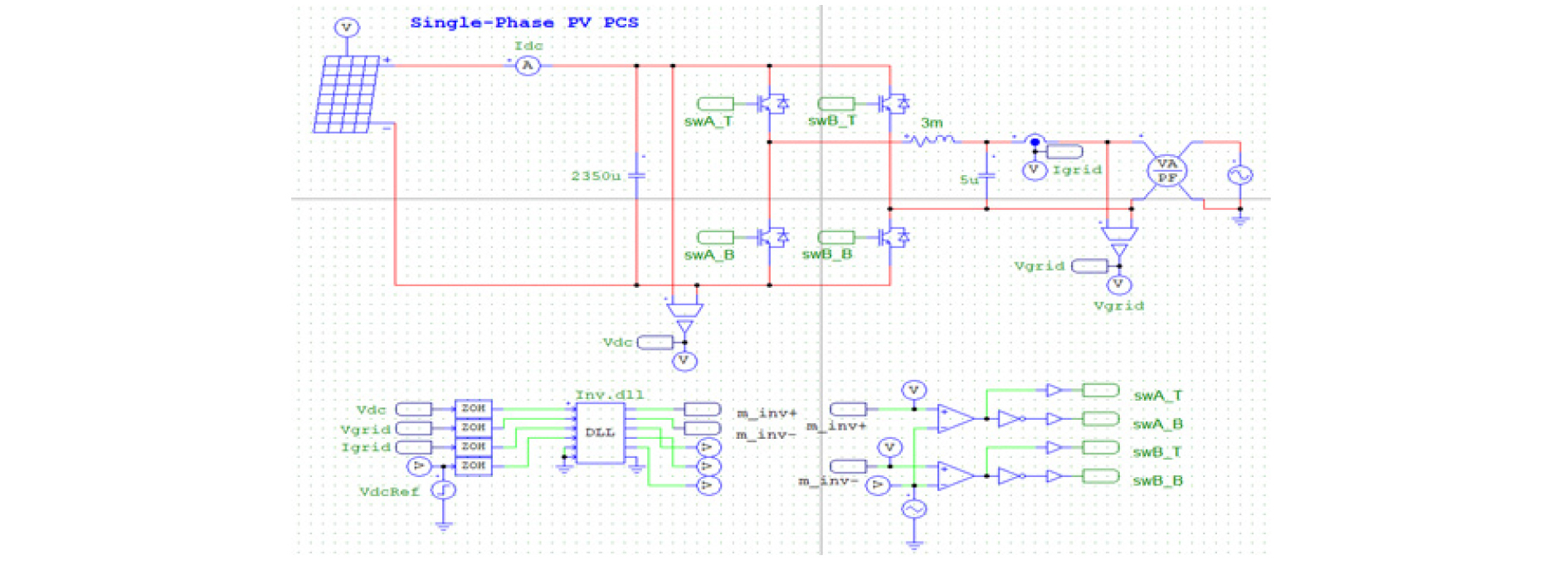

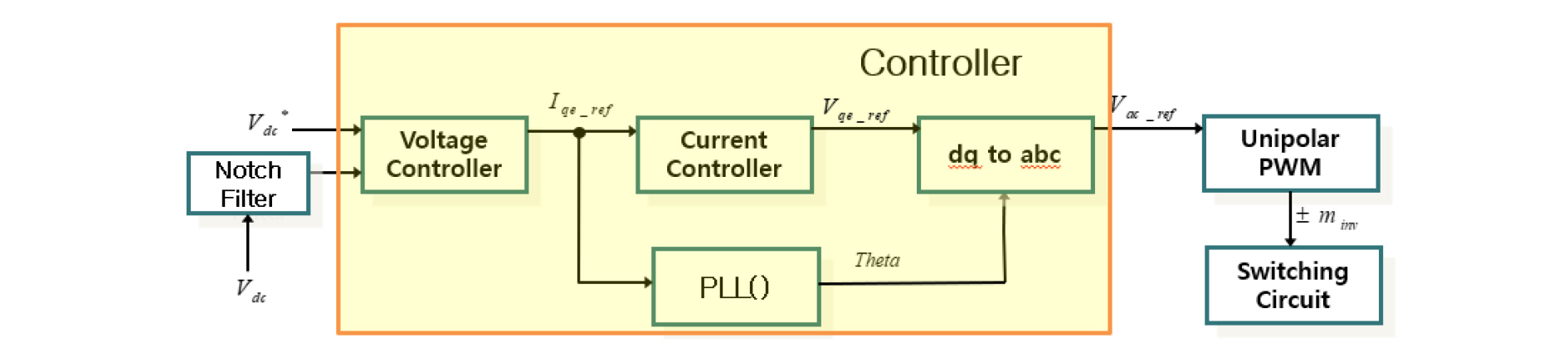

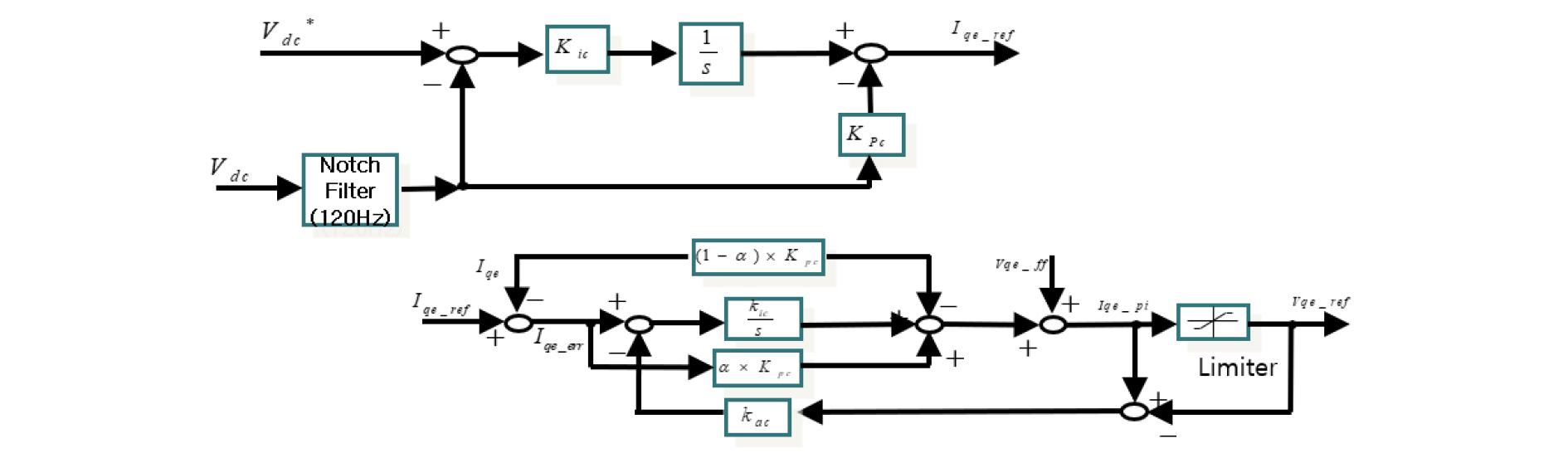

Fig. 5는 PSIM을 이용해 단상 PVPCS 회로를 구성했으며 제어기는 전압 제어기와 전류 제어기를 이용해 PVPCS를 제어했다. Fig. 6은 전체 제어기의 블록도이고 Fig. 7은 전압 제어기와 전류 제어기의 블록도이다. 전압 제어기의 경우 dc-link 커패시터 충전 시 Overshoot가 적게 발생하는 IP 제어기를 사용했으며, 전류 제어기의 경우 PI - IP 제어기를 사용해 값에 따라 PI, PI – IP 혼합, IP 제어기로 동작하게 했다4. 본 논문에서는 로 설정해 PI 제어기로 시뮬레이션을 진행했다.

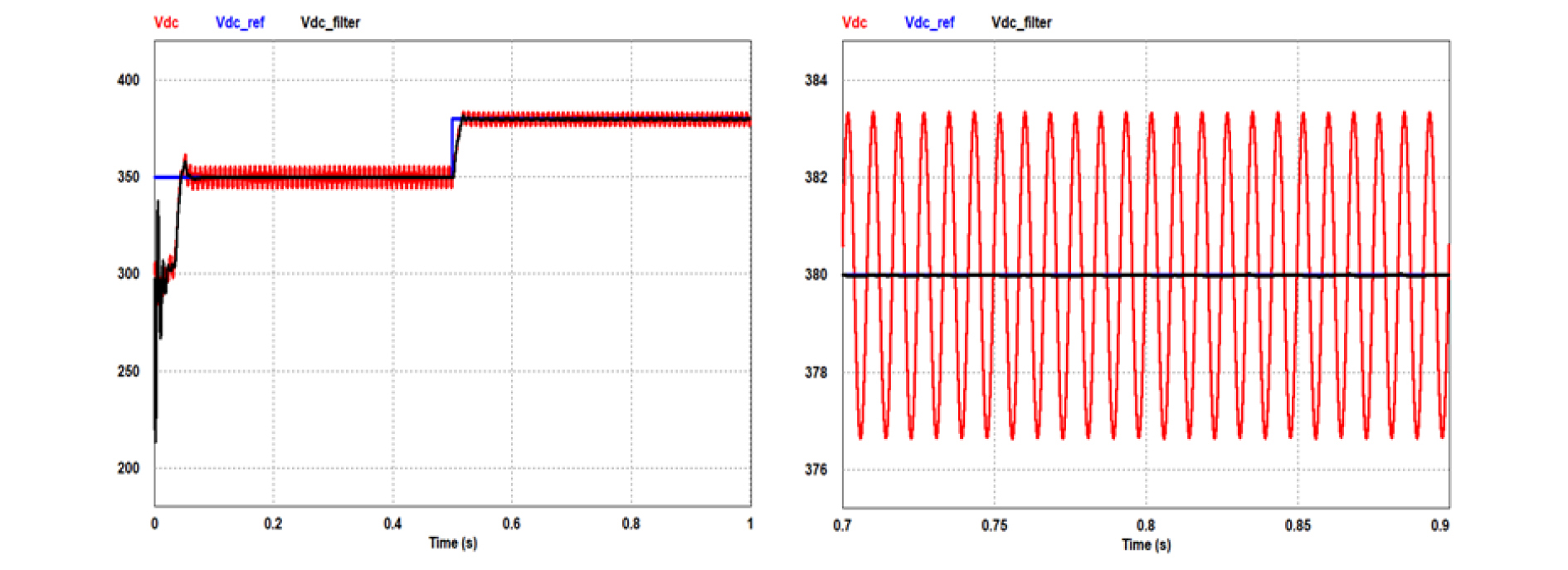

Fig. 8은 PVPCS를 실제 dc-link 단 커패시터 전압 제어 시 전압 지령 값 , 실제 전압 , 노치 필터가 적용된 전압 의 파형을 나타낸다. 0.5s에서 를 350 V에서 380 V로 설정했으며 파형을 통해 전압 제어가 이뤄짐을 확인했다. 또한 Fig. 8의 오른쪽 파형은 0.7 ~ 0.9s로 확대한 것이며 파형을 통해 노치 필터가 적용되어 120 Hz의 AC 리플이 제거됨을 알 수 있다.

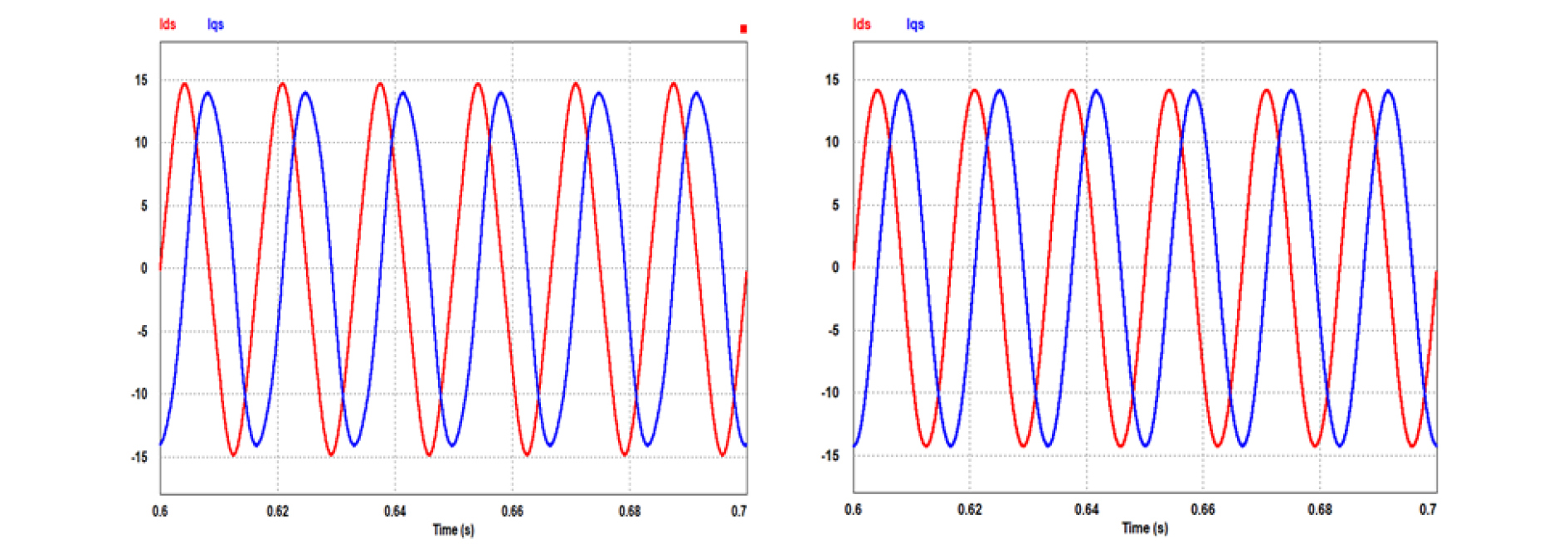

노치 필터 적용 전/후를 비교하기 위해 전류 제어기의 를 확인했다. Fig. 9의 왼쪽 파형은 노치 필터를 적용하지 않았을 때이며, 오른쪽 파형은 노치 필터를 적용했을 때의 의 파형이다. 노치 필터 적용 전인 왼쪽 파형에서는 120Hz AC 리플에 의해 와 의 파형의 크기가 같지 않지만 노치 필터 적용 후 와 의 파형의 크기는 같음을 확인할 수 있다. 이는 에 의해 출력된 전압 제어기의 전류 지령에 왜곡이 존재하지 않기 때문이다.

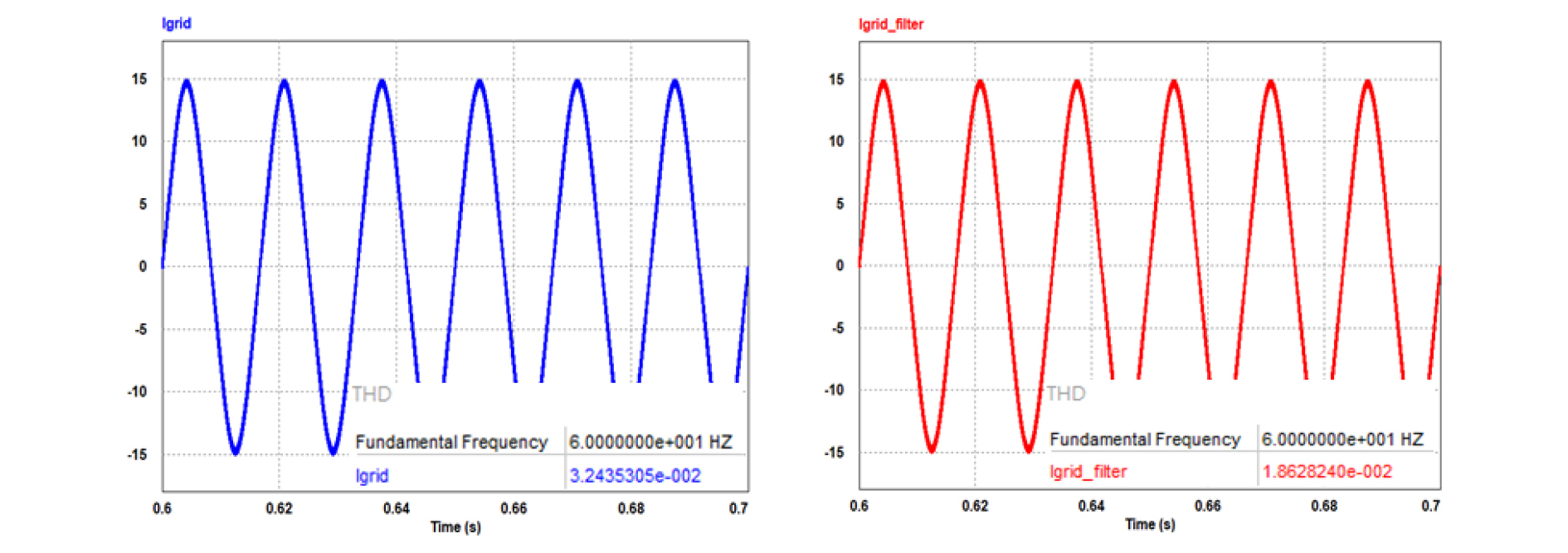

또한 PVPCS의 출력 전류를 통해 노치 필터 적용 전/후를 비교했다. Fig. 10의 왼쪽 파형은 노치 필터 적용 전 출력 전류의 파형과 THD이며, 오른쪽 파형은 적용 후 출력 전류의 파형과 THD를 나타낸다. 노치 필터를 적용한 경우 출력 전류의 THD가 1.86%로 적용 전보다 1.38% 개선된 것을 확인할 수 있다.

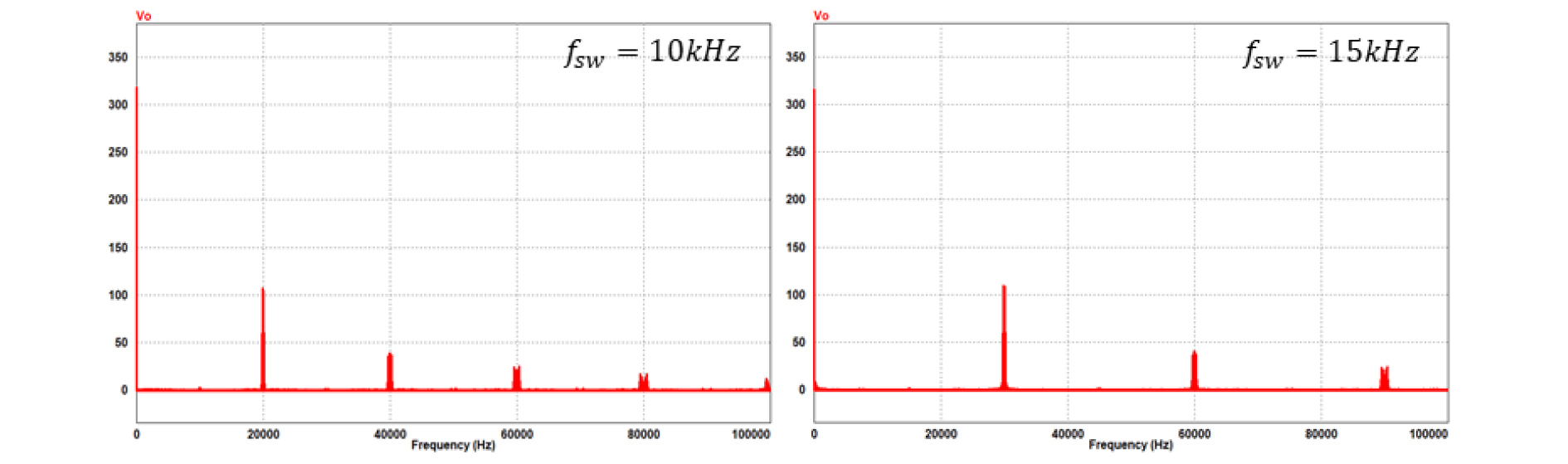

스위칭 주파수 에 따라 출력 전압의 고조파 차수가 결정된다. Fig. 11에서 가 10 kHz 일 때와 15 kHz 일 때의 출력 전압의 FFT를 확인했다. Unipolar PWM의 경우 차 고조파가 가장 크며 가 클수록 고조파 차수가 커지므로 작은 LC 필터에 의해 쉽게 필터링이 이뤄지지만, 스위칭 손실이 크게 발생한다. 반대로 가 작을수록 고조파의 차수는 작아져 상대적으로 큰 LC 필터가 필요하지만, 스위칭 손실은 적게 발생한다. 따라서 노치 필터를 적용한 PVPVS에서 스위칭 손실에 의한 효율의 감소가 크지 않으며 작은 LC 필터를 사용하는 적절한 를 설정하는 것이 중요하다.

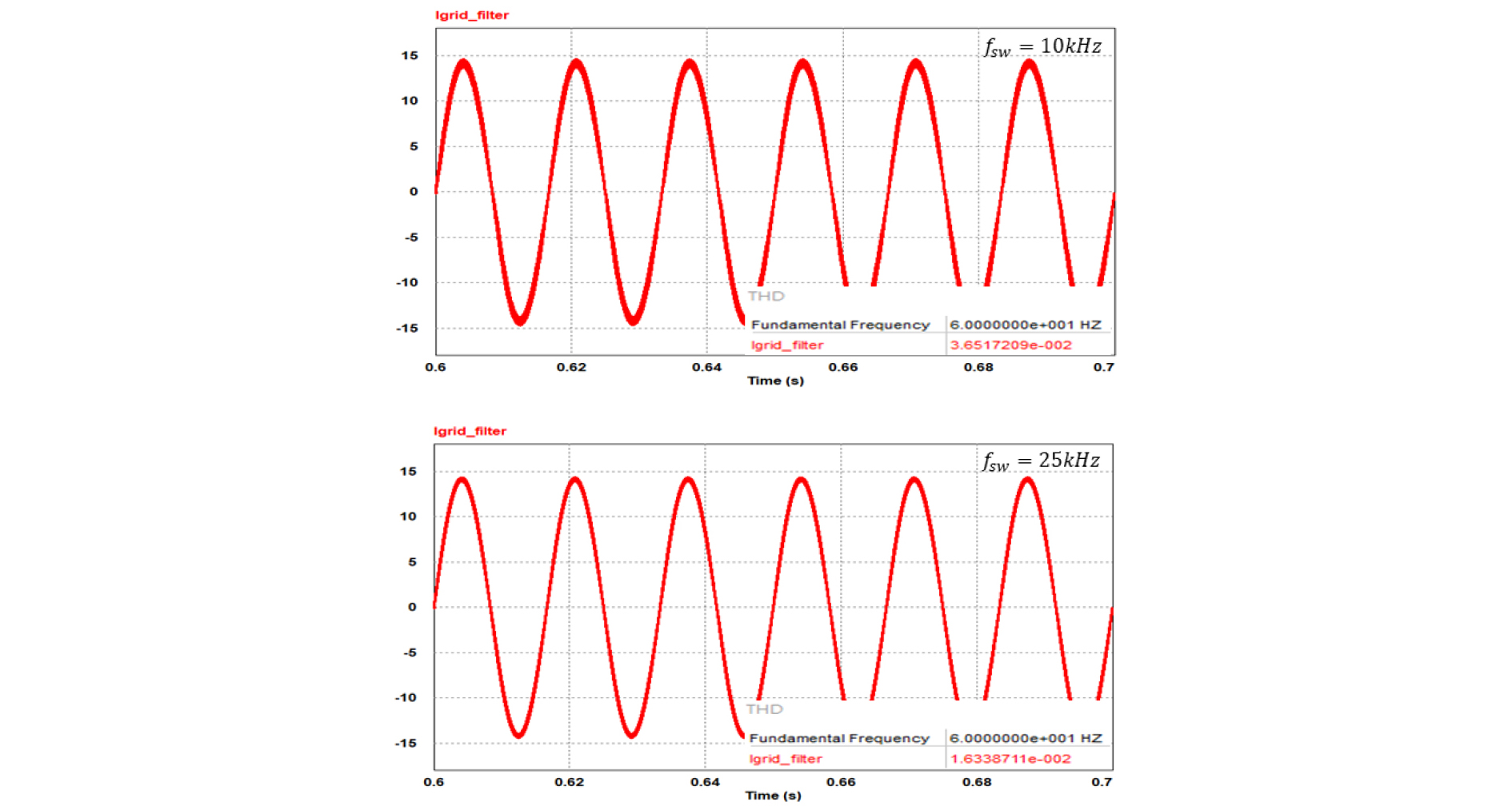

Fig. 12는 가 10 kHz와 25 kHz 일 때 노치 필터가 적용된 PVPCS의 출력 전류와 THD를 나타낸다. 10 kHz일 때 출력 전류의 THD는 3.65%이며 25 kHz일 때 출력 전류의 THD는 1.86%로 1.79%의 차이가 발생한다. Table 3은 노치 필터가 적용된 PVPCS에서 를 10 kHz, 12 kHz, 15 kHz, 18 kHz, 20 kHz, 23 kHz, 25 kHz로 설정했을 때 출력 전류의 THD를 정리한 것이며 가 커질수록 THD는 감소하는 것을 알 수 있다.

Table 3 THD of output current according to switching frequency

| 10 kHz | 12 kHz | 15 kHz | 18 kHz | 20 kHz | 23 kHz | 25 kHz | |

| THD | 3.65% | 3.13% | 2.52% | 2.10% | 1.86% | 1.74% | 1.63% |

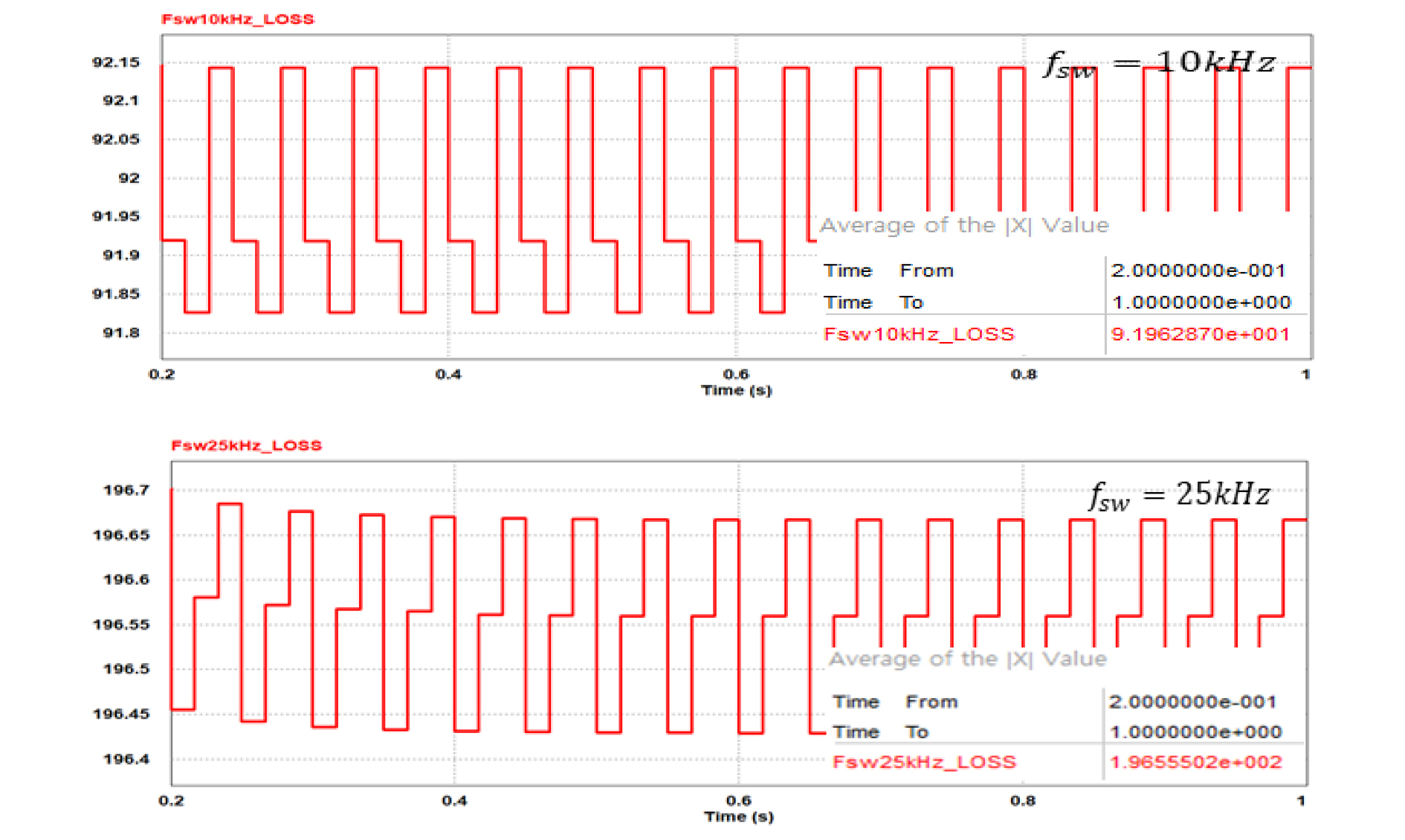

Fig. 13은 가 10 kHz와 25 kHz일 때 PSIM의 Thermal Module을 이용해 TRINNO TGAN40N60F2DL IGBT의 스위칭 손실을 확인했다5. 해당 IGBT의 datasheet를 참고하여 파라미터 설정을 했으며, 시뮬레이션 조건은 이전과 동일하게 진행했다6. 10 kHz일 때 스위칭 손실은 117.37 W이며 25 kHz일 때 스위칭 손실은 270.50 W가 발생한다. Table 4는 노치 필터가 적용된 PVPCS에서 를 10 kHz, 12 kHz, 15 kHz, 18 kHz, 20 kHz, 23 kHz, 25 kHz로 설정했을 때 스위칭 손실을 정리한 것이며 가 커질수록 스위칭 손실이 커지는 것을 알 수 있다.

Table 4 Switching loss value according to switching frequency

| 10 kHz | 12 kHz | 15 kHz | 18 kHz | 20 kHz | 23 kHz | 25 kHz | |

| LOSS | 117.37 W | 137.77 W | 168.38 W | 198.99 W | 219.32 W | 249.93 W | 270.50 W |

시뮬레이션을 통해 얻은 출력 전류의 THD와 스위칭 손실 데이터를 바탕으로 단상 PVPCS의 최적의 을 결정하기 위한 Cost function은 다음과 같이 정의할 수 있다. 우선 노치 필터의 적용 전/후에 따라 출력 전류의 THD가 영향을 받는 것을 확인하였으며 노치 필터를 적용한 PVPCS에 대해서만 구한다. 출력 전류의 THD와 스위칭 손실은 의 변수라고 할 수 있다. 결국 단상 PVPCS에서 효율에 직/간접적으로 영향을 주는 것은 크게 출력 전류의 THD와 스위칭 손실이라고 할 수 있다. 출력 전류의 THD에 의한 효율의 변화는 스위칭 손실에 의한 변화보다는 상대적으로 작지만 효율의 측면에 있어서는 무시할 수 없다. 이러한 점을 바탕으로 출력 전류의 THD가 낮을수록 Cost function은 증가하고 스위칭 손실이 커질수록 Cost function은 감소해야 하므로 각각의 계수는 시뮬레이션 데이터를 기반으로 계산했다. 최종적으로 식(10)과 같은 Cost function을 나타낼 수 있다.

| $$F(f_{sw})=\frac{1.05}{THD_{f_{sw}}}+\frac{98.85}{LOSS_{f_{sw}}}$$ | (10) |

식(10)를 이용해 의 변화 따른 Cost function을 계산하면 10 kHz와 20 kHz일 때 높은 값을 갖는다. 하지만 가 2배 증가해도 스위칭 손실의 증가가 크지 않으며 또한 크기가 작은 LC 필터를 사용하여 필터링이 이뤄진다는 점과 출력 전압 질의 향상으로 인해 출력 전류의 THD의 감소에 따른 효율이 증가하므로 단상 PVPCS의 최적의 는 20 kHz로 정할 수 있다.

5. 결 론

본 논문에서는 단상 태양광 인버터가 계통과 연결해 단상 PVPCS로 동작하는 경우 dc-link 커패시터의 전압에 계통에 의한 120 Hz AC 리플이 발생하며 노치 필터를 이용해 리플을 제거하였다. 노치 필터를 이용해 120 Hz AC 리플을 제거하는 것만으로도 PVPCS의 출력 전류의 THD가 낮아짐을 확인했다. 또한, 스위칭 주파수 의 변화에 따른 출력전류의 THD와 전력용 반도체 스위치의 스위칭 손실을 시뮬레이션을 통해 확인함으로써 Cost function을 제안하였고 최적의 스위칭 주파수 를 확인했다. 향후 계획으로는 실험을 통하여 본 논문에서 제안한 Cost function을 증명해 보이도록 하겠다.